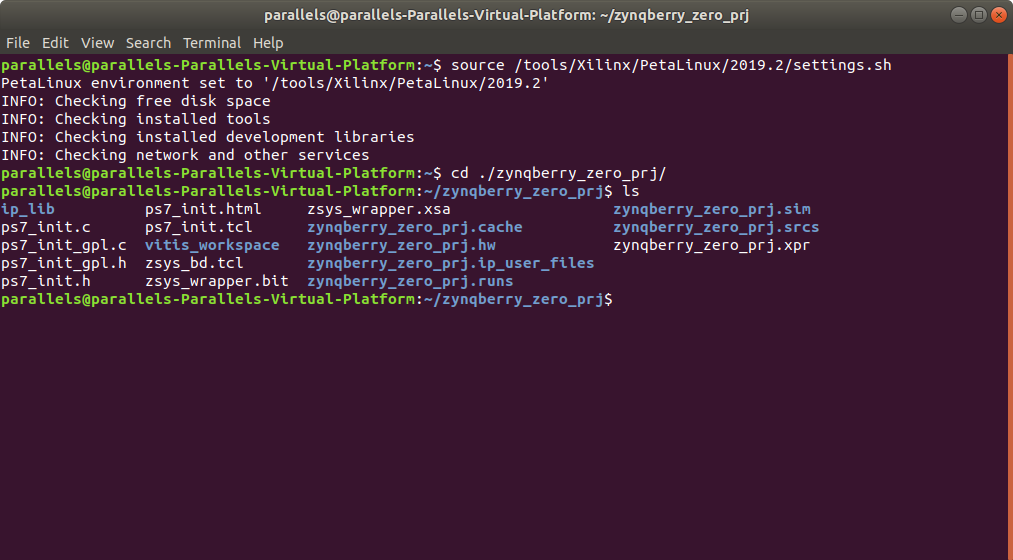

Petalinux-create -t project –template zynqMP -n ultra96v2-petalinuxĤ- Go to the generated project folder and configure the project Source /home/opt/petalinux/2019.2/settings.shģ- In the “ultra96v2-vitis-pkg” folder create a PetaLinux project

ultra96v2.xsa 2- Linux OSġ- Go to the “ultra96v2-vitis-pkg” folder generated in the first step (i.e., 1-XSA design) and run the followoing commandsĢ- Run the setting.sh file located at the PetaLinux installation folder by running this command Write_hw_platform -include_bit ultra96v2.xsaĢ6- You can validate the generated XSA file by running the following TCL command. and run the following TCL command to generate the XSA file Go to “ultra96v2-vitis-pkg/vivado” that you have created. you can use pwd command to check the folder. And from the popup menu select “Create HDL Wrapper… ” and select the “Let Viviado manage wrapper and auto-update” option in the dialog box.Ģ5- Then under the PROGRAM AND DEBUG option in the left-hand side panel, select “Generate Bitstream” and wait until the end of the process.Ģ5- After generating the bitstream, go to the TCL Console view and make sure you are in the right folder. And from the popup menu select “Generate Output Products…”.Ģ3- Select the Generate button and wait for the process to finish.Ģ4- Again, press the right-click on the “ultra96v2_design (ultra96v2_design.bd)” option in the source view panel. Set_property fault_output_type “sd_card” Ģ1- Press the right-click in Diagram view and in the popup menu select Validate Design.Ģ2- Press the right-click on the “ultra96v2_design (ultra96v2_design.bd)” option in the source view panel. Set_property sign_intent.datacenter false Set_property sign_intent.external_host false Change ids of clk_out2, clk_out3, and clk_out4 to 1, 2, and 3, respectively.ġ9- In the xlconcat_0 interfaces, enable In0, Int1, Int2, Int3, Int4, Int5, Int6, Int7, which are interrupt interfaces.Ģ0- Go to the “TCL Console” view and run these commands Note, to change the id filed you must press the Enter key on your keyboard. (Window–>Platform Interfaces).ġ5- Click on “Enable platform interfaces” if this the first time you select the Platform Interfaces option in the project.ġ6- By write click on each option and select Enable to enable the following interfaces:ġ7- Enable the following clock interfacesġ8- Select the enabled clk_out1 and in the Options window change the id to 0 and select the is_default. For this purpose, select “Platform Interfaces” option from the “Window” menu in the Vivado IDE.

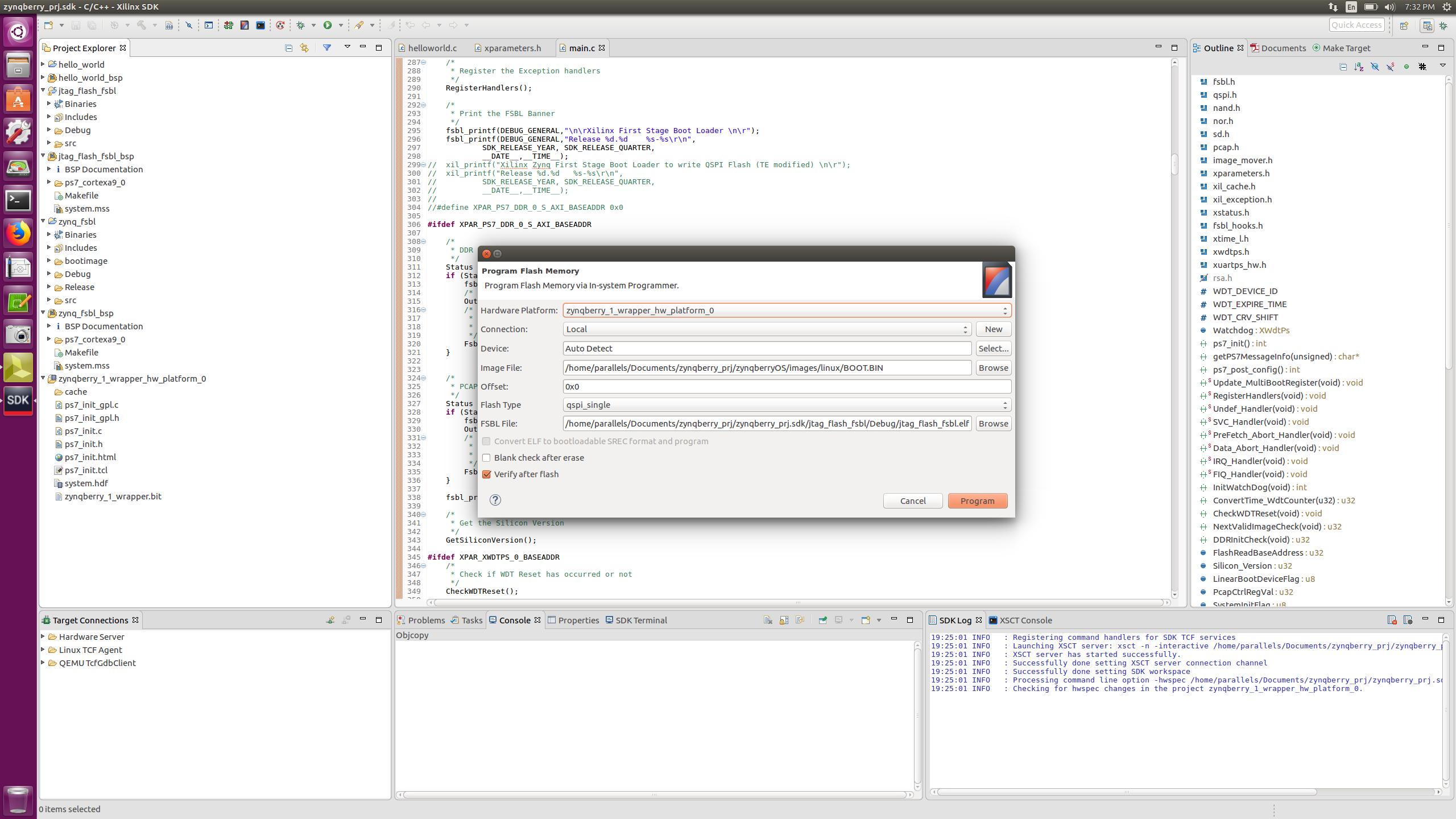

Figure 16 Figure 17ġ4- Now, we should declare the platform (PFM) interface and properties. Figure 14ġ3- Configure the added IP as Figure 16 and connect that to the Zynq as shown in Figure 7. Figure 13ġ1- Add connections as Figure 14. Figure 12ġ0- Add four Processor System Reset IPs corresponding to four output clocks. Add four output clocks and make sure that the reset type is “Active Low”. Figure 11ĩ- Double click on the added IP and configure that as Figure 12. Figure 9ħ- Double click on the Zynq IP and configure that as Figure ? Figure 10Ĩ- Add a Clocking Wizard IP to the design. Figure 7ĥ- Add a Zynq UltraScale+ MPSoC IP into the Diagram view Figure 8Ħ- Click on “Run Block Automation” and make sure the “Apply Board Reset” is selected. Figure 1 Figure 2 Figure 3 Figure 4 Figure 5 Figure 6Ĥ- In the Vivado project, create a block design with the name ultra96v2_design. Figures 1-6 show the flow of the project creation. 1- XSA designġ- create a directory called ultra96v2-vitis-pkgģ- Run Vivado and create a project called ultra96v2-xsa in the ultra96v2-vitis-pkg/vivado folder. To make Vivado detects the board, copy the Avnet ultra96v2 board definition files (at here) to the /data/boards/board_files.

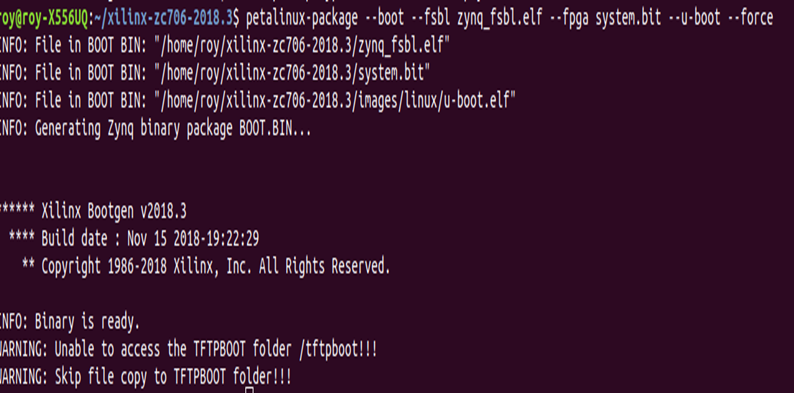

#Linux boot.elf binary which is created by petalinux install#

Note that, the Xilinx Vitis software includes Vivado, so you do not need to install that separately. I have installed Xilinx Vitis and Petalinux 2019.2 under the Ubuntu 18.04 OS. In the sequel, I am trying to briefly explain each step. Test– Create a simple application to test the generated platform.Create Platform – Using Xilinx Vitis to generate the Platform.

0 kommentar(er)

0 kommentar(er)